|

1 �� ��

�������Ŵ���(Low Noise Amplifier��LNA)�����M��Ƶ����ϵͳ�д���ǰ��λ�ã�������ָ��ĺû��Խ��ջ����������кܴ��Ӱ�졣�����������[1]�������ɶ༶�Ŵ�����ɵĽ���ϵͳ������������ϵ��������ȡ����ǰ���Ŵ���������ϵ�������͵أ����ջ����յ��ź�ǿ����-120��-20 dBm֮�䣬���Ϊ������ϵͳҪ��LNA��Ҫ������Ҫ��

(1) �ṩ���ʵ�����Ŵ��źţ��Լ�С������·��ϵͳ������Ӱ�졣

(2) �ڷŴ�������������뾡����С���������ź�ʧ�档

(3) ���бȽϺõ����Զȡ�

(4) ���������ʵ��50 ���迹ƥ�䡣

������У�������������������ָ��ﵽ���ţ�����ͨ������ʵ�֡���Ϊ��Щ����ָ�������ǣ�ơ�Ӱ�죬��ʱ����ì�ܡ��������ƹ�������β�������ԭ���˸���ָ������Ϊ��Ҫ�ġ�

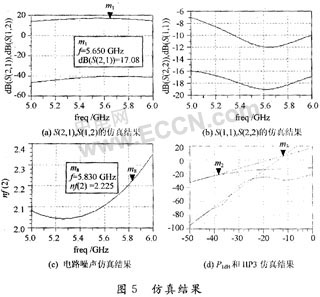

�������Ӽ����IJ��Ϸ�չ��MOS���������ߴ粻�ϼ�С�����CMOS�����Ѿ��ﵽ0.1 ��m���£�MOS�����ĸ�Ƶ����Ҳ��˵��Ը��ƣ���ֹ����Ƶ���Ѿ��ﵽ200 GHz���ϡ���ʹ��CMOS���յĹ���Ƶ���Ѿ��ﵽGHzƵ�ε���Ƶ���ɵ�·(GHz RFIC)��Ҫ�����䱾���־��еͼ۸��ĺ��ɶȵ��ص��Լ��ͻ������ֵ�·�Ĺ�����������տ���ʵ��Ƭ��ϵͳ(SoC)���ص㣬ʹ�����ֹ�����ʵ��GHz RFICʱ�����Լ۱���ӵ�����Ե����ơ�D.K.Shadfer��T.H.Lee���ʵ��������GPS��1.5 GHz��CMOS�������Ŵ�����C.S.Kim��������0.8��m CMOS�������ʵ���� 1.9 GHzȫ���ɵ������Ŵ�����Wenjun Sheng���˲���0.35 ��m CMOS���������Ӧ����Bluetooth�Ľ��ջ�����Wang Wenqi����0.25 ��mCMOS������Ʋ������˹�����2.4 GHz��ȫ���ɵĵ������Ŵ��������IJ���TSMC0.18��m CMOS RF���������һ������������Ƶ��Ϊ5.7 GHz�ĵ������Ŵ�����ʹ��ADS���еĵ�·��������������5.4��5.8 GHz����ƹ���Ƶ���ڣ�S21�ﵽ17 dB��S11С��-11 dB������ϵ��С��2.2 dB�����Զ�ָ��IIP3Ϊ-11.6 dBm��������·����0.65 V�ĵ�Դ���磬ֱ�����Ľ�Ϊ3 mW���ܺܺõ�����͵�ѹ�����ĵ�Ҫ��

2 ��·�ṹ���

2.1 ����ƥ��

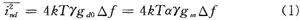

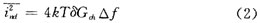

��ͼ1(b)�У�©��������������Ϊ��

ʽ�У�gd0ΪԴ©��ѹƫ��Ϊ0ʱ��©������絼��gmΪMOS�ܵĿ絼����Ϊ�빤�ա�ƫ����صij�����ֵ��2�M3��2֮�䣬a=gm�Mgd0<1��

��Ƶ�ʽϸߵ������£����뿼�Ƿ���̬ЧӦ����ʱ��MOS�ܵĹ�����դ��������Ϊ�ֲ�ʽ����-�������硣MOS�ܵ�դ����Դ��֮�䲻���Ǵ������ԣ������ڵ�Ч�����絼Gch��һ���棬������������ͨ��դ��������ϵ�դ�����γ�դ��������������ֵΪ��

ʽ�� ��CgsΪMOS�ܵ�դ����Դ�����ݣ�&Ϊ�빤�ա�ƫ����صij�����ֵ��4�M3��15�M2֮�䡣դ�����������빵��©������������Դ��ͬ�����ߵ����ϵ��Ϊ�� ��CgsΪMOS�ܵ�դ����Դ�����ݣ�&Ϊ�빤�ա�ƫ����صij�����ֵ��4�M3��15�M2֮�䡣դ�����������빵��©������������Դ��ͬ�����ߵ����ϵ��Ϊ��

���ڳ��������Σ�c=j0.395�������ǹ����絼��������ƥ���Ӱ��ʱ����Դ����и�����ƥ��ṹ�У�����Դ�����Ls��դ�����Lgʵ���迹ƥ�䡣��ͼ1(a)��ʾ��������迹Zin������ʽ������

�������źŽ�Ƶ��Ϊ��0����г�����·ʹ֮�ڹ���Ƶ�ʴ�����г���У�

��ʱ�����迹Zin����ʽ(6)������

����������迹RsΪ������(50 ��)���Ϳ�ʹ�����ƥ����50 ����

2.2 �Ŵ��·�ṹ

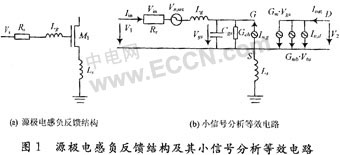

����CMOS���յĵ������Ŵ������һ����þ���Ĺ�Դ��դ�����ṹ����ͼ2��ʾ�����ֽṹ�����ڼ�С����ЧӦ�����ӷ������ȡ����й�ԴMOS��M1��Ϊ���Ŵ�ܸ���·�ṩ�㹻�����棬��դ��M2������СM1��Cgd1�����MillerЧӦ�Լ���ǿ������·�ķ���������ܡ�

���ڹ�Դ��դ�ṹ�����Ч�絼Ϊ��

��ʽ(7)�п��Կ�������С��Lsֵ���Ի�ýϴ�����棬����ͬʱҲ��ʹ�������迹Զ��50 ����ƥ��㣬����һ����Ȼ�Ľ������ʹ��S11��ֵ�������뷴��������ͱ�ȻҪ�����Ƕ��ڸ��������ۺϿ��ǡ�

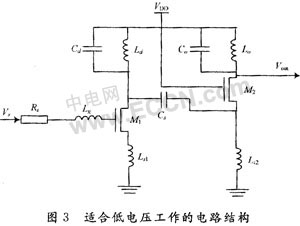

Ϊ����Ӧ�͵�ѹ��Ҫ���Բ���ͼ3��ʾ�ĵ�·���ڷ�����ԭ���Ķ�ջ�ṹ֮�õ�·�ṹ�ܹ���0.65 V�ĵ͵�ѹ�¹�����

3 ����ѡ�������������

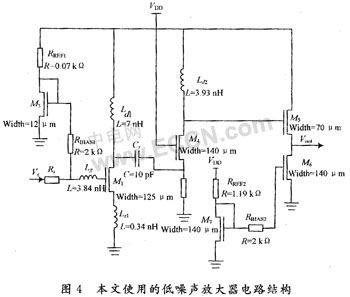

�˴�����Ƶĵ������Ŵ�����·ԭ��ͼ��ͼ4��ʾ�����а�����ƫ�õ�·��������弫����������[1]��M1�ܵ�դ����Ϊ125��m��M2��դ����M1��ͬ��

4 �� ��

���ĸ�����һ���ʺ�0.65 V������ѹ�ĵ������Ŵ�����ƣ�ʵ����������·������ﵽ��17 dB����������ƹ���Ƶ��(5.4��5.8 GHz)�ڣ�S11<-11 dB��S22<-16 dB����·��1 dB����ѹ����P1dBΪ-38.4 dBm��������IIP3Ϊ-11.6 dBm����·��ֱ�����Ľ�Ϊ3 mW������Ŀǰ�������ĵķ�չ���ơ�

���ߣ���ε������ְҵ����ѧԺ ���� ���� 414000

|