|

1 引言

目前,定时计数及控制电路大多采用单片机外加输入/输出接口电路构成。本文采用TTL集成电路设计倒数计数器,具有工作稳定、抗干扰性强、无需单片机开发系统和编程、易于制作、时间设置范围广、操作方便等优点,适用于竞赛类时间控制、烹饪定时等,也可用作实验计数器。

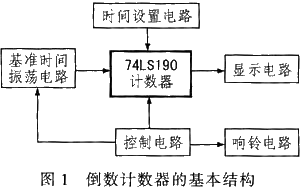

2 倒数计数器的基本结构

倒数计数器可预置“10-90”范围时间,其基本结构如图1所示,核心是TTL集成电路74LS190,该器件是可预置的十进制同步加/减计数器。倒数计数器主要由时间设置电路、基准时间振荡电路、计数器、显示电路和控制电路及响铃电路等组成。其中,基准时间振荡电路产生计数脉冲,在控制电路作用下计数器开始减1倒数计数,并显示时间变化。当显示从预置的时间变化到全“0”时,计数器停止计数器,同时响铃电路响铃提示。

3 倒数计数器电路设计

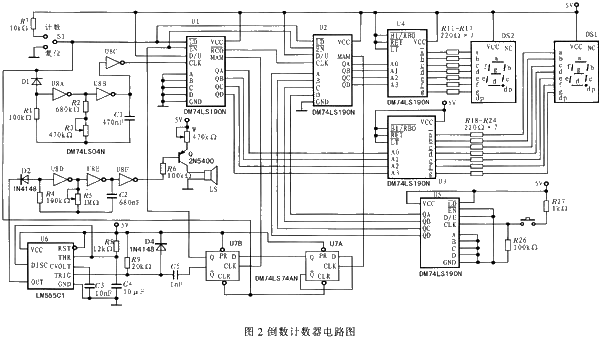

倒数计数器的电路如图2所示。计数器和时间设置电路由器件74LS190、74LS74双D触发器以及555时基电路构成控制电路,74LS04六反相器构成基准时间振荡电路和响铃振荡电路。

3.1 时间设置电路

图2中U5(74LS190)及外同电路组成时间设置电路,S2是时间设置按钮,74LS190的LD端接高电平,EN和D/U端接低电平,CLK端接计数时钟脉冲,对时钟脉冲上升沿进行加法计数,每按一次S2按钮,产生一个高电平的时钟脉冲。QA~QD输出相应的“0~9”递增可循环BCD码,该BCD码送至U2的A~D预置端。当S1接至复位端时,U2的QA~QD输出为预置的A~D端的BCD码,该码经U4(74LS47)的译码驱动数码管DS2,显示预置的倒数时间的十位数值,而显示个位数值的DS1则由U1的A~D预置端决定,该值始终处于“0”,因此,每按下一次S2,DS2、DS1显示“00~90”可循环变化的倒数时间。

3.2 基准时间振荡电路

U8(74LS04)中三个反相器及外围电路组成时间振荡电路,U8A和U8B构成多谐振荡器,振荡周期T=2.2C1(R2+R3),该时间振荡脉冲经U8C反相缓冲后作为计数脉冲送至U1的CLK端。D1是控制多谐振荡器起振二极管,当S1开关处于复位端时,振荡器停振,U8C输出为高电平;而当S1处于计数位置时,振荡器开始振荡,输出基准时间脉冲送至U1倒数计数开始。U8B和U8C振荡波形如图3所示。

3.3 计数及显示电路

U1~U4以及DS1~DS2组成了计数显示电路。当S1开关处于复位时,U1和U2的LD端处于低电平,U7的D触发器复位,输出Q端为低电平送至U1和U2的EN端,因此,74LS190处于预置输出状态,U2的QA~QD输出为U5预置产生的BCD码,此码经U4的74LS47 BCD-7段译码后,直接驱动数码管DS2共阳极的进行显示倒数时间的十位数值。而显示个位数值的DS1则由U1的A~D预置端决定,该预置值始终处于“0”。当S1开关处于计数端时,LD端由低电平跳变为高电平,由于D/U端接高电平,U1和U2开始进行减计数。由于U1的预置值为“0”,在每一个基准时问振荡电路发送时钟脉冲上升沿,U1进行减1计数.输出为“0-9-8――1-0”循环变化的BCD码,经过U3译码后,直接驱动数码管DS1显示。而U1每次减1计数到全“0”时,纹波时钟输出端RCO产生一个脉冲,送至U2的CLK端,作为十位数的计数时钟脉冲。在时钟脉冲的上升沿,U2对预置的BCD码进行减l计数,而当U2减数计数到“0”且U1也减去计数到“0”时,此时DS2,DS1显示为“00”,U7的D触发器输出高电平,U1和U2的EN端由低电平跳变为高电平,计数器停止计数,而且保持输出“0”。

3.4 控制及响铃电路

U6(LM555时基电路)、U7(D触发器)和U8(三个反相器)组成的多谐振荡电路构成了计数控制及响铃电路。U7A的D触发器构成了双稳态电路,当U2十位减1计数到“0”时,进位/借位端MA/MI输出一个高电平脉冲,作为双稳态电路的发时钟脉冲,U7A输出状态翻转,由低电平跳变为高电平,送至U7B的D触发器的输入D端。而此时,U1个位计数器再次从“9-8---1-0”循环计数,当减1计数到“0”时,U1的MA/MI端输出一个高电平,作为U7B的D触发器的时钟脉冲,因此D触发器输出Q端由低电平跳变为高电平,使得U1和U2的EN端由低电平跳变为高电平,计数器停止计数,而且保持输出“0”。Q由高电平跳变为低电平,经过由R9和C5组成的微分电路产生一个低电平脉冲触发U6的单稳态电路,U6输出由低电平跳变为高电平的暂态过程,经过T=1.1R8・C4的时间,高电平的暂态过程结束跳变为低电平,在暂态高电平期间,U8D~U8F组成的多谐振荡器开始振荡,经过放大后驱动扬声器LS响铃。

4 电路调试

该电路设计只需调试基准时间即可,R3选用精密微调电阻,频率计接至U8C输出端,S1开关打至计数端,微调R3使频率计显示的周期为1 000 ms。响铃频率可断开D2调节R5,直至得到合适的铃声为止。

5 倒数计数器应用

此电路设计非常适用于现场竞赛定时,主持人预先设置所需时间,将S1打至复位,连续轻按S2设置时间。若需设为60 s,则需连按6次S2,显示为60,表示60 s。当主持人要求竞赛者定时回答问题时,主持人或其他工作人员立即将S1开关打至计数端,此时,计数器开始工作,时间显示从预置时间开始倒数显示,当显示为“0”时,响铃电路产生约3 s的结束铃声。当需下一次开始时,再将S1打至复位,重新开始。此外,该设计电路也可作为家庭烹饪定时器,需将定时10 s~90 s扩展到10 min~90 min,将C1用10μF代替,R2和R3用MΩ代替,调节R3使周期达到1分钟即可。为了使响铃连续报警,可去掉图2中U6单稳态电路,将U7B的D触发器Q端直接连到D2的阴极,这样在定时时间达到,响铃电路一直报警直至将S1打至复位为止。

6 结束语

基于TTL集成电路的倒数计数器,电路设计简单,调试方便,时间设置范围广,还可以根据需要将倒数时间设置到个位,只需再增加一个74LS190和设置开关,将设置的个位数值时间送至U1即可。

|