|

l 引 言

模数转换电路作为模拟技术与数字技术的接口广泛应用与工业控制、雷达、通信、消费电子等许多领域。随着数字技术、软件无线电和微电子技术的高速发展,极大地促进了模数转换电路设计技术的发展,高速、高性能的数据采集(A/D变换)系统占据了越来越重要地位。如果想对模拟信号进行数字信号处理,A/D变换是必不可少的。在雷达系统中,他把接收机输出的模拟信号转化为数字量以供后面的DSP进行处理,是构成信号处理系统前向通道的核心,其性能的高低某种程度上决定着整个处理系统性能高低,因而可以说在一定程度上决定了整个雷达系统的性能。基于现代A/D在整个系统的重要地位,高速、高性能的数据采集(A/D变换)系统的实现方法愈来愈重要了。本文以美国AD公司生产的A/D变换器AI)924.0和美国Xilinx公司生产的FPGA XC4013为例,阐述了一种高速、高性能的数据采集系统的实现方法。

2 模数转换器AD9240

2.1 内部构造

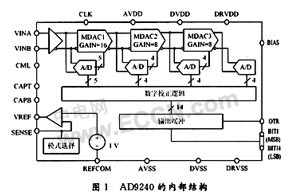

AD9240是美国AD公司近年推出的一种转换速率为10 MHz、单工作电源的14位并行模/数转换集成电路。他是一个完整的单片ADC电路,片内有高性能、低噪声的SHA采样保持电路和输出缓冲器以及可选择的内部或外部基准源。AD9240采用带有数字输出误差校正的多级差动流水线结构,确保在宽温度环境下工作不丢码。图l是AD9240的内部结构框图。

2.2 工作时序

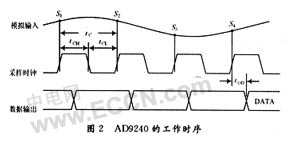

AD9240在每个时钟周期都允许捕捉到新的输入采样,但是实际上他需要3个时钟周期完成转换的整个处理过程,并将数据输出。如图2所示。这种延迟考虑在瞬时数据采集和实时存储的情况下是非常重要的。

所有高速高分辨率的A/D对输入采样时钟的质量都很敏感。AD9240的输入时钟最好满足占空比45%~55%的条件,对于采样时钟低于10 MHz的情况,占空比可以偏离此范围,但必须满足tCH和tCL的要求。

2.3 输入输出

AD9240的输入模拟信号幅度VP-P可以选择。AD9240有一个片内基准源,通过管脚连线可选择基准为1 V或2.5 V。如果SENCE管脚与REFCOM管脚相连,VREF电压为2.5 V。如果SENCE管脚与VREF、管脚相连,VREF电压为1 V。VREF、管脚的电压决定了A/D变换器满量程输入幅度,满量程输入幅度为2倍的VRE[7。

AD924O的数字输出在整个输入范围内采用正逻辑的自然二进制编码。

3 现场可编辑门阵列XC4013

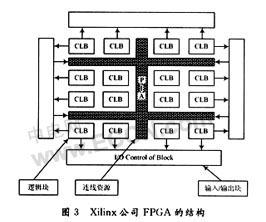

XC4013是美国Xilinx公司生产的FPGA芯片,他的最大逻辑门数可达13 000门,结构可以分为3个部分:可编程逻辑块CLB(Configurable Logic Blocks),构成了器件的逻辑核心;可编程I/O模块IOB(Inptlt/Output Block),连接逻辑块的互连资源;可编程内部连接PI(Programmable Intercon-nect),用于逻辑块之间、逻辑块与输入/输出块之间的连接。CLB在器件中排列为阵列,周围环形内部连线,IOB分布在四周的管脚上。Xilinx的CLB功能很强,不仅能够实现逻辑函数,还可以配置成RAM等复杂的形式。

FPGA器件的功能由逻辑结构的配置数据决定。工作时,这些配置数据存放在片内的SRAM或者熔丝图上。使用SRAM的FPGA器件,在工作前需要从芯片外部加载配置数据。配置数据可以存储在片外的E2PROM或其他存储体上,人们可以控制加载过程,在现场修改器件的逻辑功能,即所谓现场编程。通过对FPGA编程可以很方便地实现时序控制和数据存储。

4 数据采集系统的实现

4.1 系统构成

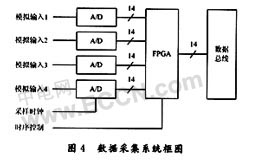

在雷达系统中,经常需要对多个不同距离目标进行实时采集和信号处理,这就需要对大量的数据进行存储。本文以4片AD9240和1片xC4013所组成的数据采集系统为例说明其实现方法。

图4是本文介绍的数据采集系统的框图,他主要由4片ADC和1片FPGA构成。4片AD9240对4路模拟信号同时进行采样,其中每一路模拟信号都可以包含N个不同距离的目标回波,数据采集系统可以将这N个模拟信号快速地转换为数字信号的同时将这些数据锁存在FPGA中,之后按照信号处理所需的模式传送出去。

由于AD9240的最大转换速率为10 MHz,因此N个目标回波之间的时间间隔应≥100 ns;而因为XC4013的内部资源所限,一般情况下N≤8。

4.2 测试结果

在频域测试中,以信噪比和有效位数来衡量转换电路的噪声情况。在输入信号频率为20 KHz,采样速率为10 MHz情况下,对A/D变换输出数据进行64点FFT分析,结果其信噪比SNR为73 dB,平均噪声基底为-76 dB,,

5 结 语

根据测试分析以及实际应用,现对高速模数转换电路的设计提出下列参考意见:

根据ADC手册的要求连接模拟地和数字地,通常将模拟地和数字地分别连接,在远端共接;模拟电源与数字电源应作隔离处理,以减少对模拟电路的干扰。采用电源层和地层,并利用其将模拟信号线和数字信号线隔离,这样可以避免数字电路中的干扰串入模拟电路中影响转换性能。ADC器件输出端应采用数据锁存器,既起到隔离驱动的作用又便于数据的输出。选取合适的运算放大器减少谐波失真。信号线尤其是模拟输入信号线应尽量短粗,并进行大面积覆铜,以减少信号失真及其之间的相互干扰。尽量保证采样时钟的精度,减少时钟抖动对转换性能的影响。

作者:马军,中国电子科技集团公司第20研究所陕西西安,710068

|